# EE 505

# Lecture 20

### ADC Design

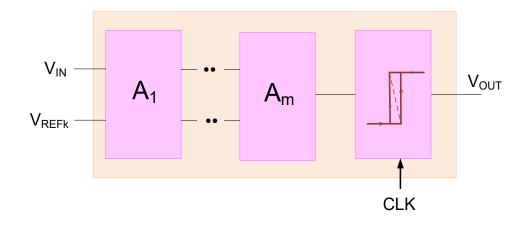

- The Flash ADC

- Comparators

- Interpolating ADCs

- Folded ADCs

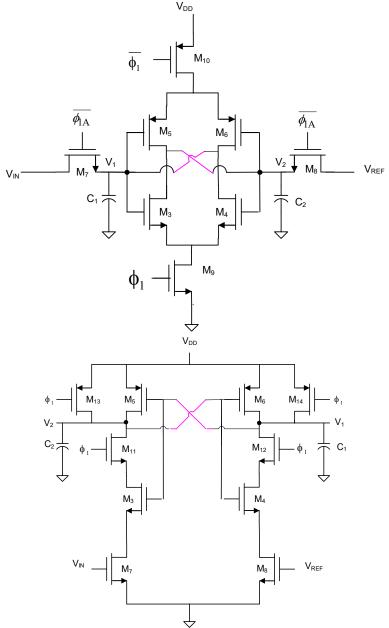

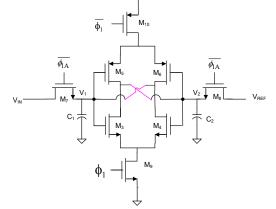

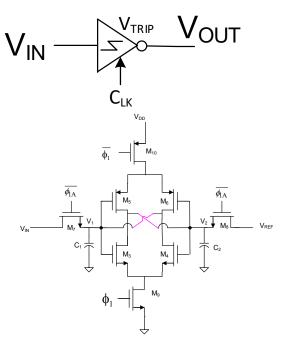

# Clocked Comparator with Regenerative Feedback

# Clocked Comparator with Regenerative Feedback

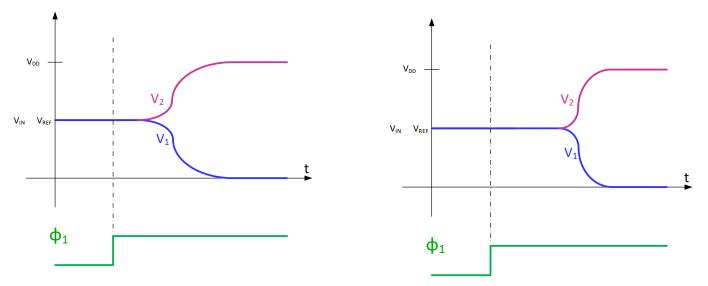

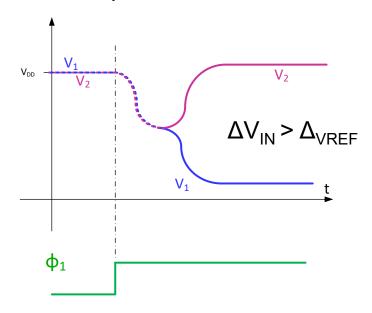

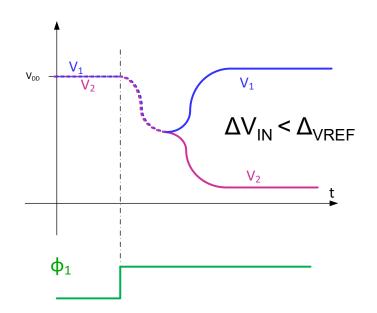

when  $V_{\text{IN}}$  and  $V_{\text{REF}}$  close to each other

- decision delayed

- may stay in metastable state until after decision must be made

- vulnerable to making wrong decision due to offset or noise

#### Ideal Responses

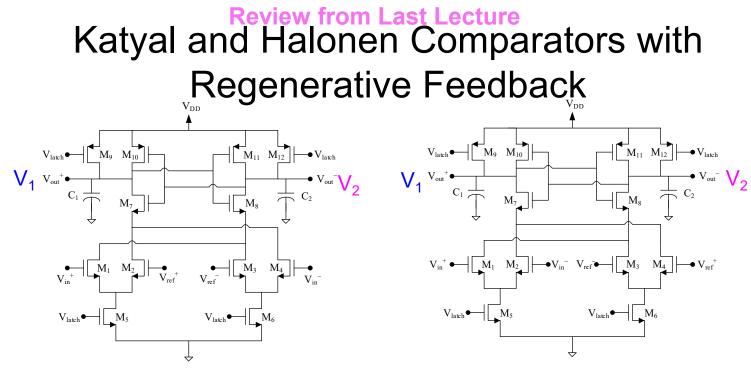

#### **Review from Last Lecture**

Where are poles of regenerative comparators located?

In RHP !

Is stability of concern?

No! Want positive real axis poles (i.e. unstable circuit) to force decision

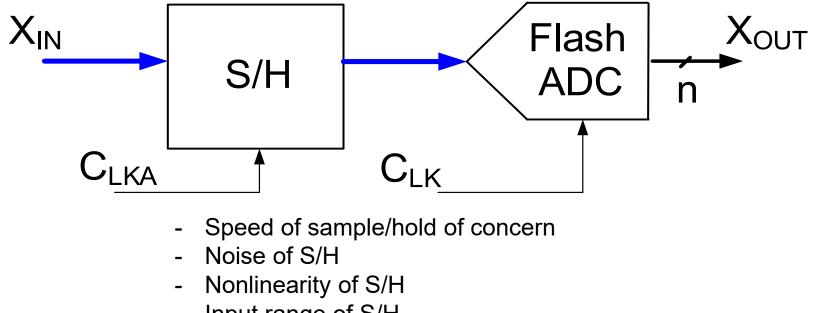

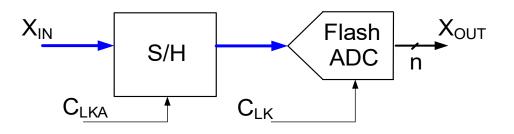

Front-End S/H can mitigate effects of input change during conversion

- Input range of S/H

- Power dissipation of S/H

- Loose asynchronous operation of ADC

- Widely used

- S/H may be most challenging part of design

### Will discuss input S/H later

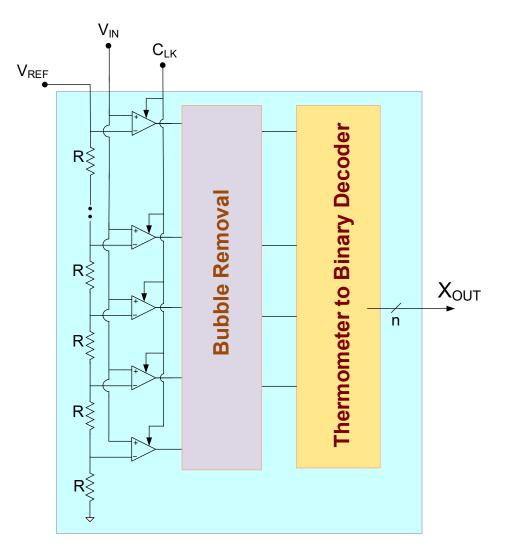

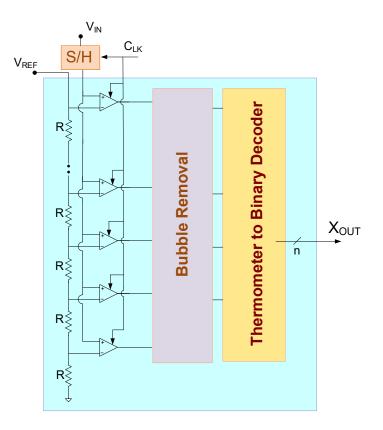

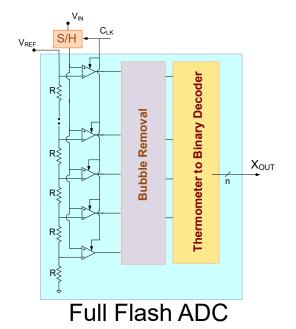

# Flash ADC

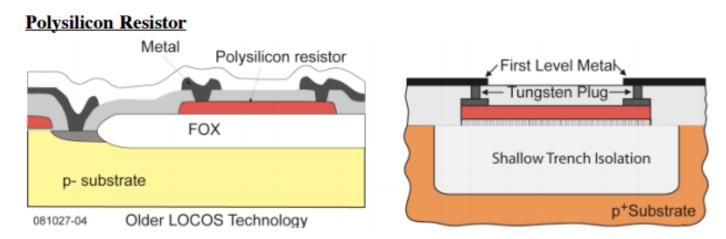

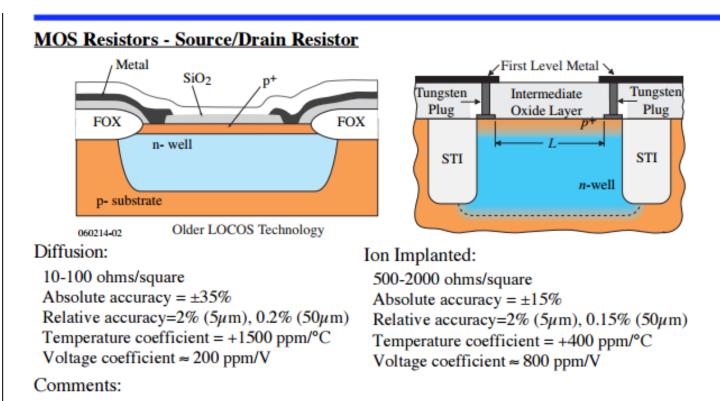

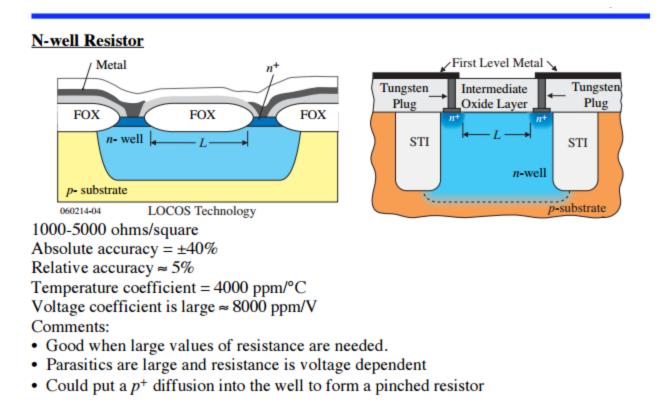

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

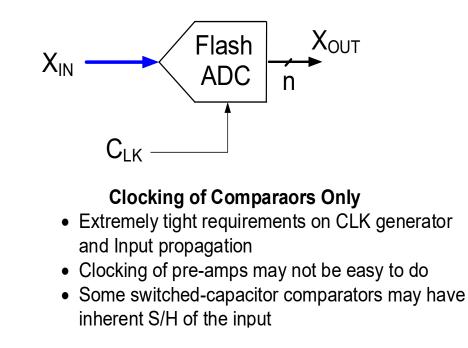

Can we clock only the comparators in a Flash ADC thereby eliminating the S/H?

Clock of Comparators only instead of input S/H in Flash ADC

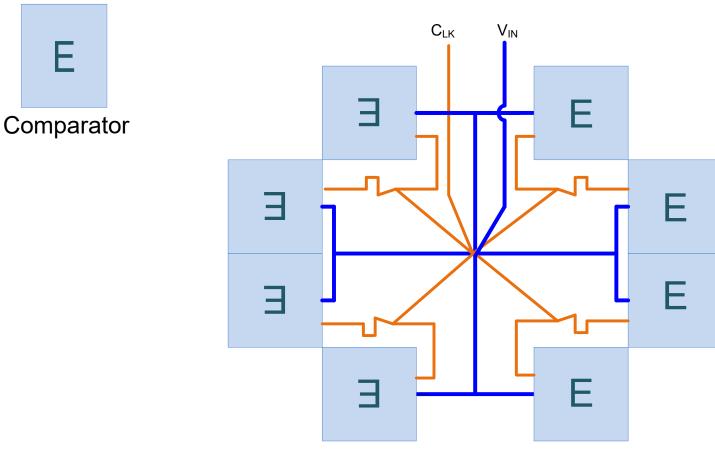

Routing of Clock and Input is Critical

Symmetric Equal Path Length Layout

Path length of V<sub>IN</sub> and C<sub>LK</sub> need not be identical but convenient if they are Have maintained minimal overlap of V<sub>IN</sub> and C<sub>LK</sub>

Routing of Clock and Input is Critical  $C_{\mathsf{LK}}$  $V_{IN}$ Ε Ε F F Ξ Ε Ξ

Symmetric Paths for  $V_{\text{IN}}$  and  $C_{\text{LK}}$

Layout challenging if resolution is very large

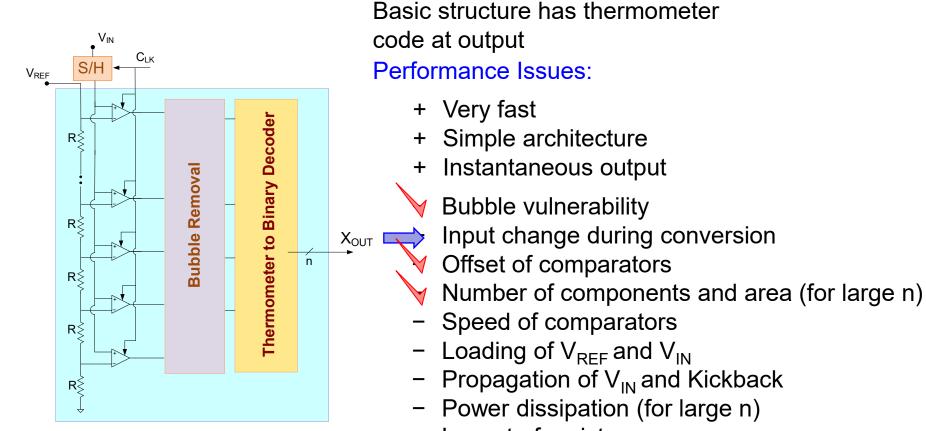

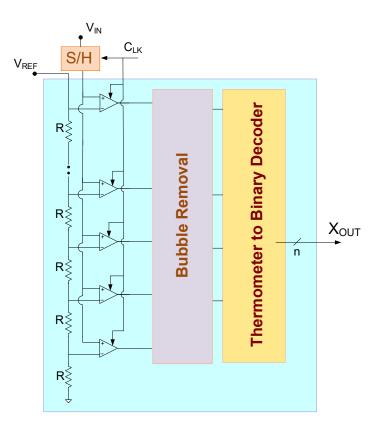

# Flash ADC

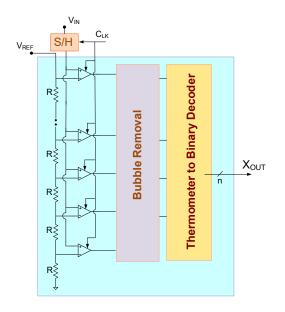

Basic structure has thermometer code at output Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

Bubble vulnerability

- Input change during conversion

- Offset of comparators

Number of components and area (for large n)

- Speed of comparators

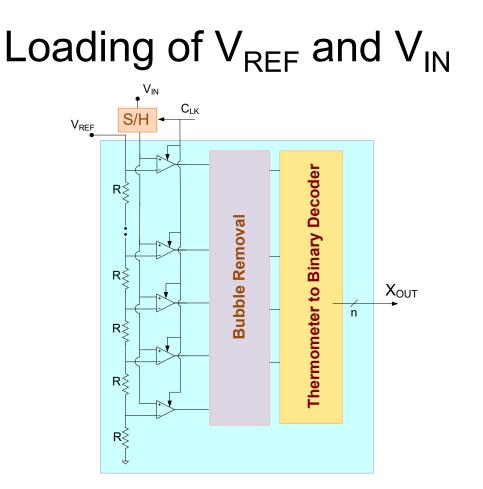

- Loading of  $V_{\text{REF}}$  and  $V_{\text{IN}}$

- Propagation of  $V_{IN}$  and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

# **Speed of Comparators**

Linear Amplifier as Comparator

- Gain may be inadequate to generate Boolean output for some inputs (metastability)

- Common-mode input varies significantly with V<sub>REFk</sub>

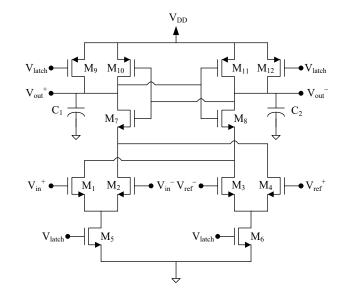

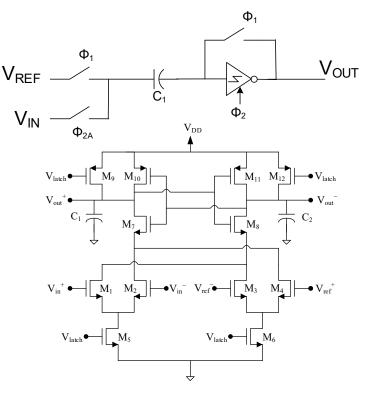

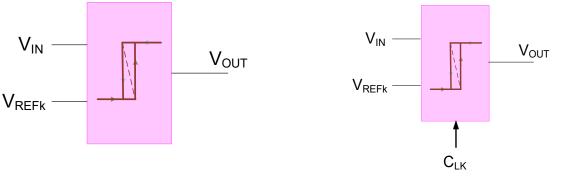

**Regenerative Feedback Comparators**

- Reduces (but does not eliminate) metastability concerns

- Common-mode input still varies with V<sub>REFk</sub>

- Offset Voltage High

- C<sub>LK</sub> can significantly improve speed

- C<sub>LK</sub> can force operation on negative slope region thereby reducing hysteresis window-induced previous code dependence

- Kickback to Input of concern

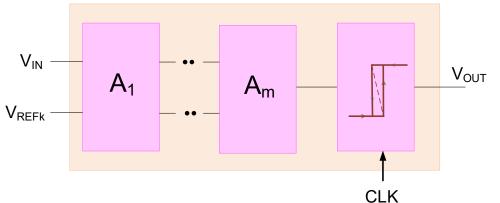

# **Speed of Comparators**

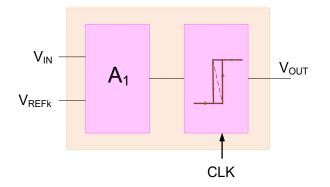

- Preamp often precedes regenerative stage

- Regenerative stage can be single-ended or differential

- Common-mode input to preamp still of concern

- Common-mode inputs of all regenerative stages can be the same

- Significant reduction in offset voltage possible

- Kickback to  $V_{\text{IN}}\,$  and  $V_{\text{REFk}}\,\text{can}\,\text{be}\,\text{reduced}$

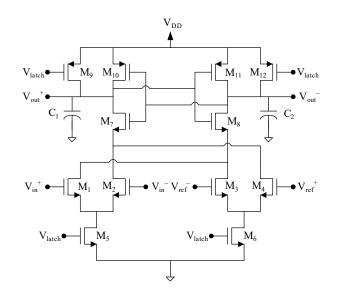

# **Speed of Comparators**

- Two or more stages of preamp gain often used

- Further reduces offset voltage and metastability concerns

- Number of stages can be selected to optimize speed and power

- Common-mode input in all stages after first can be the same

# Flash ADC

Basic structure has thermometer code at output Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

- Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- $\Rightarrow$  Loading of V<sub>REF</sub> and V<sub>IN</sub>

- Propagation of  $V_{IN}$  and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

- Capacitive load on V<sub>IN</sub> is large for large n

- Resistors in R-string small for fast recovery when V<sub>IN</sub> changes

- Inductance on bonding leads for V<sub>REF</sub> of concern if V<sub>REF</sub> externally generated

- Output impedance must remain low at high frequencies if V<sub>REF</sub> internally generated

# Flash ADC

Basic structure has thermometer code at output Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- Loading of V<sub>REF</sub> and V<sub>IN</sub>

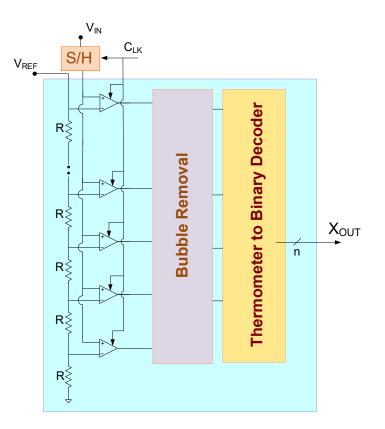

- Propagation of V<sub>IN</sub> and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

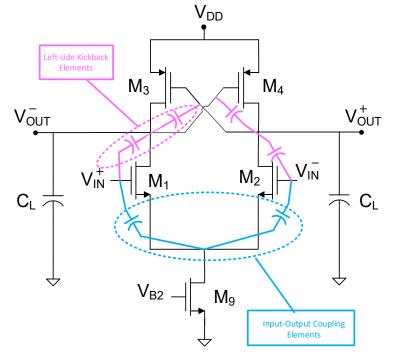

## Propagation of $V_{\mbox{\scriptsize IN}}$ and Kickback

- Key decisions being made by comparators near 0-1 thermometer code transition

- Several comparators often changing states during each conversion introducing lots of kickback

- Kickback can be reduced by introducing preamp

- Input-output coupling on each comparator introduces large transients in R-string for large input changes

- Delay in V<sub>IN</sub> propagating down string but introducing delay in clock can mitigate concern

# Flash ADC

Basic structure has thermometer code at output Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- Loading of  $V_{REF}$  and  $V_{IN}$

- Propagation of V<sub>IN</sub> and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

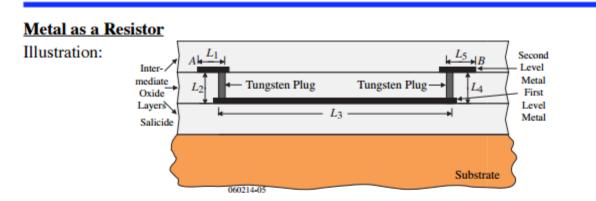

#### From lecture notes of Phil Allen

30-100 ohms/square (unshielded) 100-500 ohms/square (shielded) Absolute accuracy =  $\pm 3.0\%$ Relative accuracy = 2% (5 µm) Temperature coefficient = 500-1000 ppm/°C Voltage coefficient ≈ 100 ppm/V

#### From lecture notes of Phil Allen

- · Parasitic capacitance to substrate is voltage dependent.

- Piezoresistance effects occur due to chip strain from mounting.

#### From lecture notes of Phil Allen

Resistance from A to B = Resistance of segments  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ , and  $L_5$  with some correction subtracted because of corners.

Sheet resistance:

50-70 m $\Omega/\Box \pm 30\%$  for lower or middle levels of metal

$30-40 \text{ m}\Omega/\Box \pm 15\%$  for top level metal

Watch out for the current limit for metal resistors.

Contact resistance varies from  $5\Omega$  to  $10\Omega$ .

Tempco  $\approx +4000 \text{ ppm/}^{\circ}\text{C}$

Need to derate the current at higher temperatures:

$I_{DC}(T_j) = D_t I_{DC}(T_r)$

| $T_{f}(^{\circ}C)$ | <i>T<sub>r</sub></i> (°C) | $D_t$ |

|--------------------|---------------------------|-------|

| <85                | 85                        | 1     |

| 100                | 85                        | 0.63  |

| 110                | 85                        | 0.48  |

| 125                | 85                        | 0.32  |

| 150                | 85                        | 0.18  |

CMOS Analog Circuit Design

© P.E. Allen - 2010

#### From lecture notes of Phil Allen

#### From lecture notes of Phil Allen

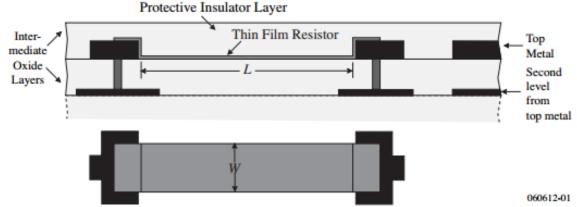

#### Thin Film Resistors

A high-quality resistor fabricated from a thin nickel-chromium alloy or a siliconchromium mixture.

Uppermost metal layer:

Performance:

Sheet resistivity is approximately 5-10 ohms/square

Temperature coefficients of less than 100 ppm/°C

Absolute tolerance of better than ±0.1% using laser trimming

Selectivity of the metal etch must be sufficient to ensure the integrity of the thin-film resistor beneath the areas where metal is etched away.

Be careful with characterization of voltage coefficients of resistors – simulators probably can not be completely trusted !

The issues:

- How is resistance actually defined when I-V relationship is not linear

- Are integrated resistors 2-terminal or 3-terminal devices?

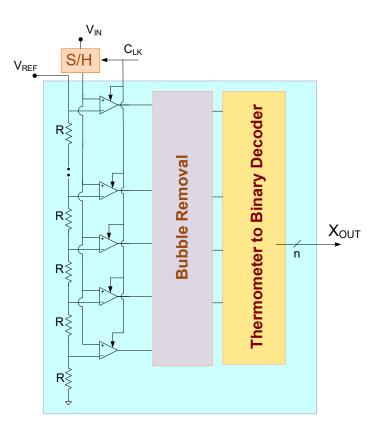

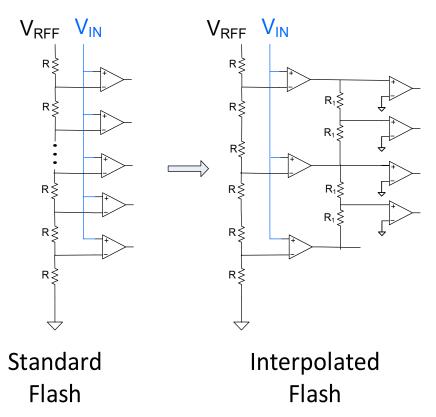

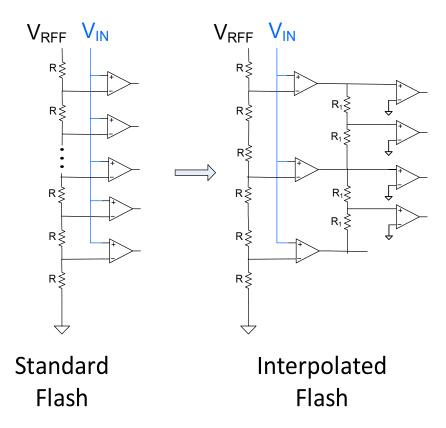

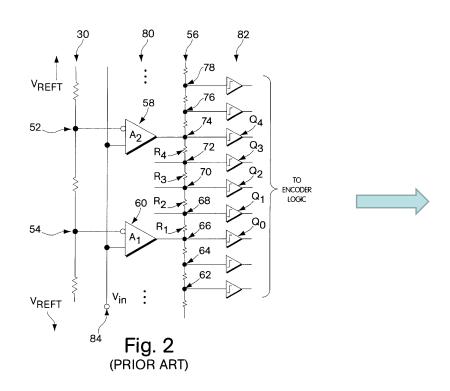

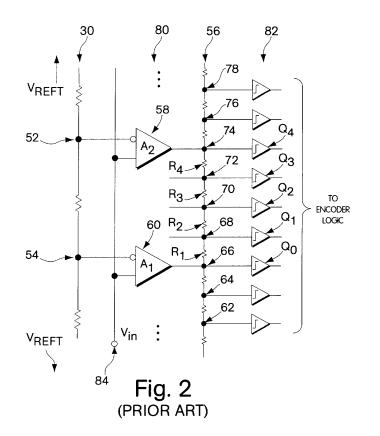

# Interpolating ADC

- Key decisions being made by comparators near 0-1 thermometer code transition in Flash ADCs

- Other comparators (away from key decision region) consume power and area but provide little useful information

- Each regenerative comparator typically requires a preamp stage(s) in full flash ADC

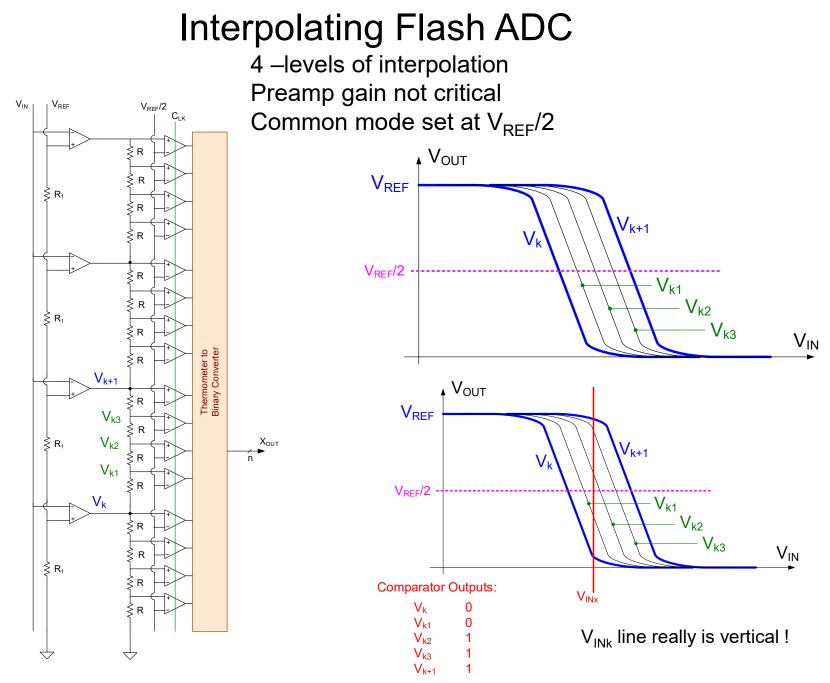

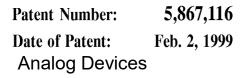

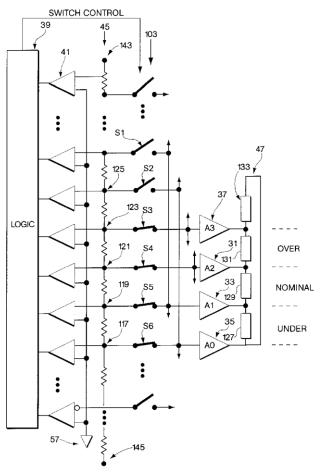

### Interpolating Flash ADC

It may appear that the number of amplifiers/comparators and resistors have been increased but ...

- First stage amplifiers/comparators can be a pre-amp

- Second stage comparators can be a latch

- Number of critical resistors in first stage has been decreased (thereby also facilitating common-centroid layout)

### Interpolating Flash ADC

- Reduction in pre-amp area and power

- Latches all referenced to ground

- Loading on V<sub>IN</sub> reduced

- Kickback to V<sub>REF</sub> reduced

- $V_{IN}$  coupling to  $V_{REF}$  reduced

- Multiple levels can be included in interpolator array

•

Standard R-String Interpolators

Flying Interpolator

Interpolator can be based upon alternative DAC structures

- Current Steering

- Charge Redistribtion

**Multi-Level Interpolators**

### Flash ADC Summary

### Flash ADC

- Very fast Simple structure Usually Clocked Bubble Removal Important Seldom over 6 or 7 bits of resolution

- Flash ADC has some really desirable properties (simple and fast)

- Wouldn't it be nice if we could derive most of the benefits of the FLASH ADC without the major limitations

To be practical at higher resolution, must address the major limitation of the FLASH ADC

Major Limitation of FLASH ADC at higher resolutions?

- Number of comparators increases geometrically --- 2<sup>n</sup>

- String DAC area increases geometrically

- Too many comparators making non-critical decisions increases power

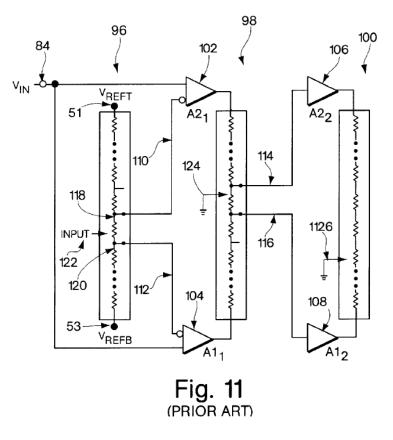

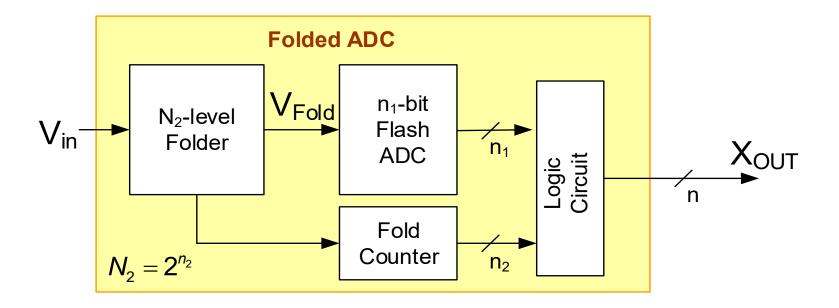

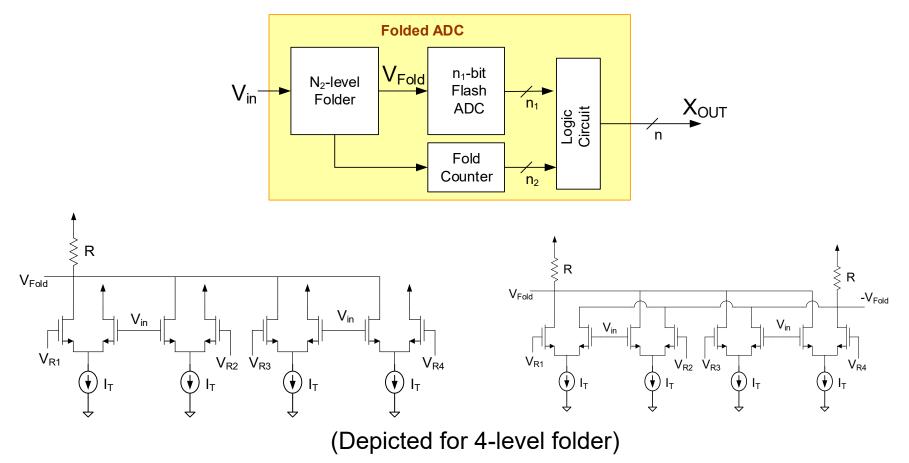

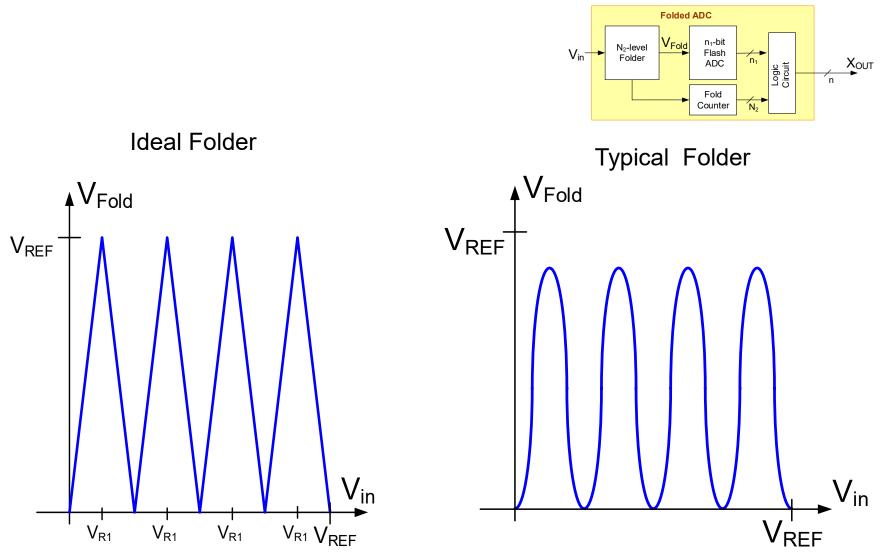

Premise: Folder provides large gain and is very fast

Similar in concept to interpolating flash ADC but

- Number of comparators has been reduced

- Thermometer to Binary decoder is eliminated

- Provides gain in each fold region

- Effective input range increased from  $V_{\text{REF}}$  to  $N_2 V_{\text{REF}}$

- Reduces performance requirements of flash ADC by N<sub>2</sub>

- Reduces number of comparators by factor of N<sub>2</sub>

- Performance strongly dependent upon performance of folder

- With fast folders, speed comparable to that of a flash ADC

- Architecture of choice by Phillips (now NXP) for high-speed operation for many years (Rudy van de Plassche)

- Competes with pipeline for performance

- Requires N<sub>2</sub> differential amplifiers

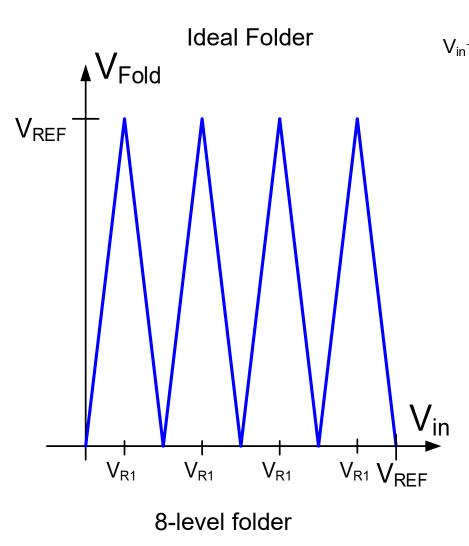

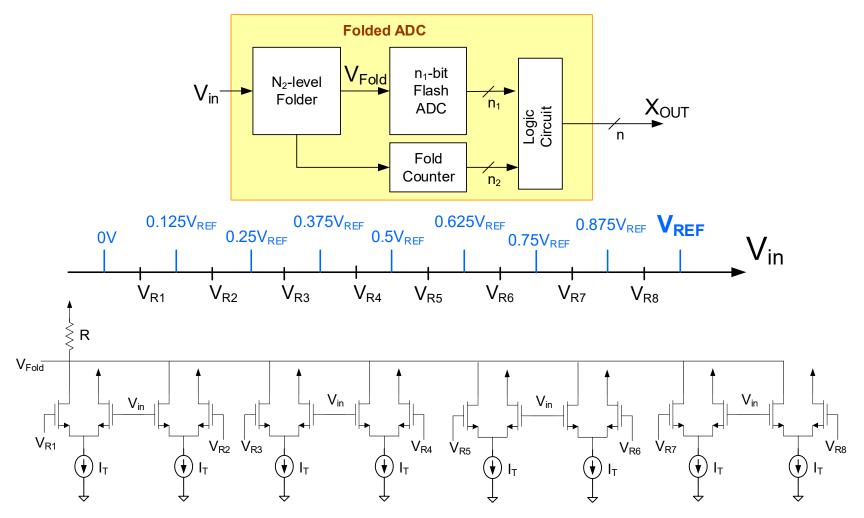

- Basic Folder Circuit (8 level)

- Simple Differential Pair can be very fast

- Usually implemented in differential form

- Differential output almost free

Nonlinearity in folder not a major problem since resolution nonlinearity affects primarily the LSBs and resolution of folded ADCs not large

# Stay Safe and Stay Healthy !

# End of Lecture 20